# **High Speed Ethernet Interface Board**

### **Key Features**

- The board has five independent nodes and each NODE incorporates a Cyclone II FPGA and Tiva Microcontroller as the core components.

- Each Node receives 15 bit parallel data along with the Return SCLK (RSCLK) and Return Transmit Clock (RTCLK) and sends it over Ethernet.

- High speed Ethernet Interface Board has two configurations C13114B-1 for Differential inputs and C13114B-2 for single ended inputs.

- Each node has 15 channels for receiving differential input and 24 channels for receiving TTL single ended inputs.

### **High Speed Ethernet Interface Board**

#### Design

Cornet's High speed Ethernet Interface Board, C13114, is an Extended Double Euro form factor board. This interface board provides the conversion of Multichannel differential parallel data into Ethernet packet data.

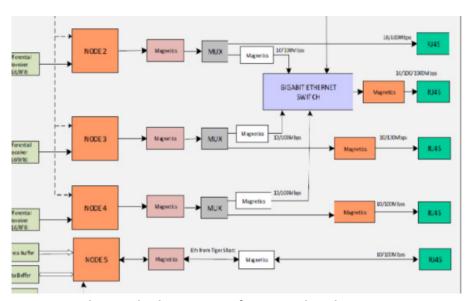

The board has five independent nodes and each NODE incorporates a Cyclone II FPGA and Tiva Microcontroller as the core components. There are also differential receivers for 16 bit parallel data and differential transceivers for transmitting and receiving TCLK (1 MHz) and SCLK (4 MHz) depending on whether it is a master or slave node.

The Tiva Microcontroller collects the parallel data and sends it over a network to the data receiver. The Tiva Microcontroller reads data over EPI (External Peripheral Interface) module implemented in the FPGA. The data is then sent as UDP over IP over Ethernet. The transmit interrupt (Packet transmit clock) is received from the FPGA.

The Node receives 15 bit parallel data along with the Return SCLK (RSCLK) and Return Transmit Clock (RTCLK) and sends it over Ethernet.

The RSCLK received from the onboard which is delayed version of SCLK determines the rate at which the data is sampled. The Tiva Microcontroller with embedded Ethernet MAC and PHY sends the data as Ethernet over IP over UDP.

Each node has 15 channels for receiving differential input and 24 channels for receiving TTL single ended inputs. These are sent to FPGA through buffers. The 24 single ended input gets divided into two 12 bits i.e. two rings (each ring has 12 bits). So, totally for 4 nodes, 60 channel differential data (4 node x 15 channel) and 96 channel single ended data (4 node x 24 channel) are received. The data is read simultaneously in 434ns duration for TTL mode of operation and 250ns duration for differential mode of operation.

### Specifications (High Speed Ethernet Interface Board)

#### **Board Specifications**

- High speed Ethernet Interface Board has two configurations C13114B-1 for Differential inputs and

- C13114B-2 for single ended inputs.

- 15 bit parallel differential input for each Node in C13114B-1 and 24 bit single ended input for each node in C13114B-2

- Node-1 work as Master mode and remaining nodes work as slave mode. Nodes can be configurable

- Each Node includes Tiva Microcontroller and Altera Cyclone II FPGA

- SDLC component is No Mount

- Ethernet output from each node supports 10/100

Mbps and Gigabit Ethernet switch output supports10/100/1000

Mbps

- Power supply input to the board is +5V and on

- board generation of voltage is +3.3V with converters

- Differential receiver for each node for inputs

- Supports 64KB DPRAM for shared memory purpose

- Extended Temperature operation range : -40 to + 85°C

- PCB form factor -Extended Double Euro card

- PCB dimension 233.4mm (H) X 220mm

(D)

## **Board Configurations/Ordering Information**

- C13114B-1 for Differential inputs

- C13114B-2 for Single ended inputs

**High Speed Ethernet Interface Board Architecture**

ISO-9001:2015 Registered